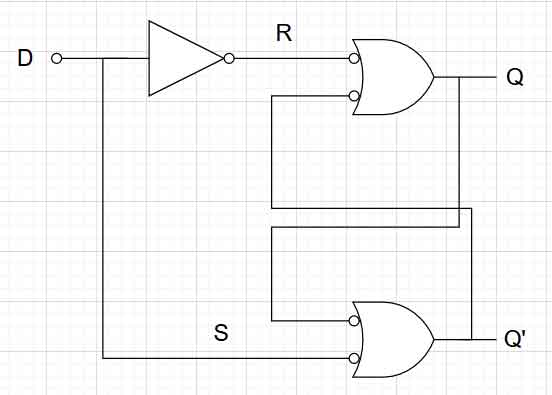

Rangkaian D Flip Flop (D FF) adalah salah satu elemen memori yang merupakan modifikasi dari RS Flip Flop. Oleh karena rangkaian RS flip flop mudah terkena keadaan tak menentu (pacu), maka dilakukanlah modifikasi rangkaian RS FF untuk menghilangkan keadaan tak menentu tersebut. Sehingga hasil dari modifikasi tersebut dikenal dengan nama rangkaian D FF (D latch) lihat gambar rangkaian D Flip Flop.

Gambar Rangkaian D Flip FLop

Tabel kebenaran D Flip Flop tanpa clock dapat anda lihat di bawah ini:

| D | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

Jika dilihat dari tabel kebenaran D flip flop tanpa clock maka dapat dirumuskan menjadi:

Q = D

Dari tabel tersebut sudah tidak terlihat lagi keadaan tak menentu atau keadaan pacu (Keadaan tak menentu adalah keadaan output atau keluaran yang hasilnya tidak tentu). D Flip Flop tanpa clock ini hampir tidak pernah digunakan dalam rangkaian.

Daftar Isi

Clock Rangkaian D Flip Flop

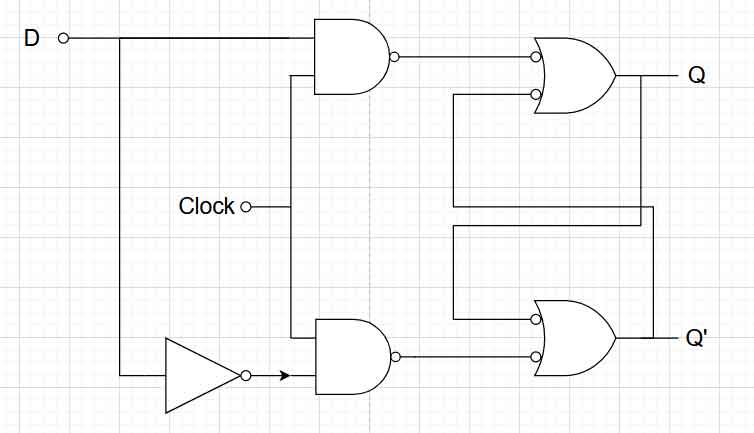

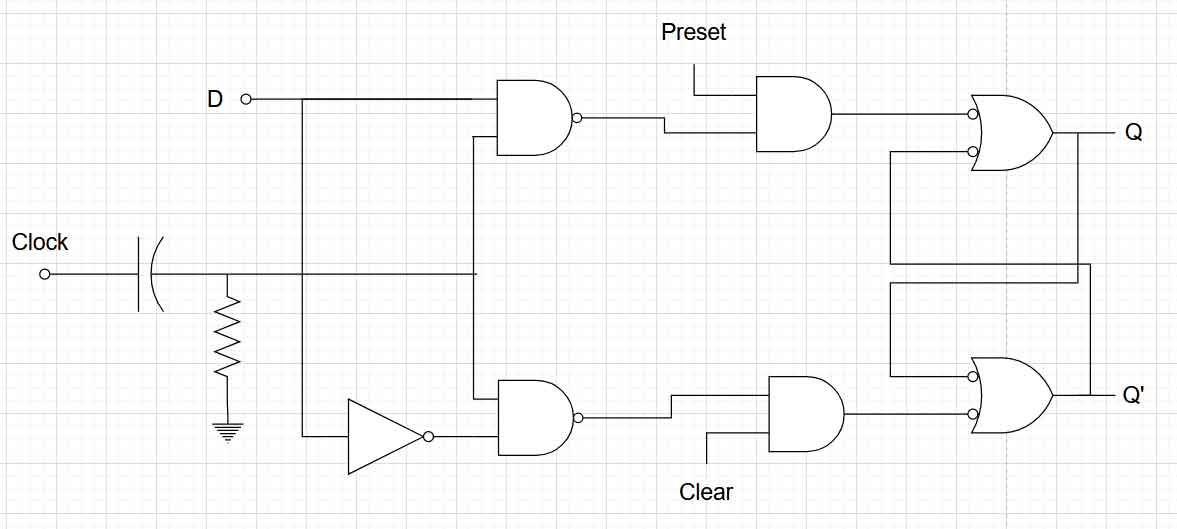

Untuk Rangkaian D FF menggunakan clock dapat dilihat pada gambar rangkaian D flip flop menggunakan clock. Input pada D FF adalah sebuah input pengontrol tunggal yang menentukan output FF sesuai dengan tabel kebenaran. Output Q pada D FF akan berada pada keadaan yang sama dengan yang terdapat pada D input jika terjadi suatu transisi positip pada Clock input.

Gambar Rangkaian D Flip Flop Menggunakan Clock

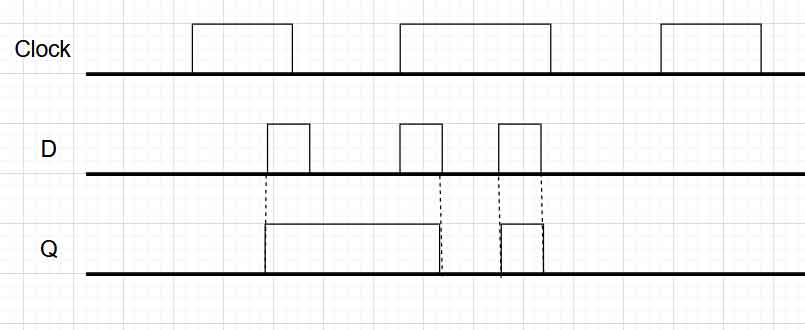

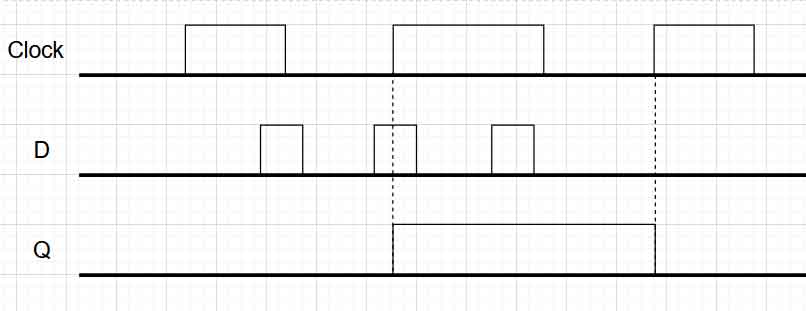

Gambar Timming Diagram D Flip Flop

Tampak dari gambar timming diagram, rangkaian D FF dengan clock akan mengontrol output tergantung dari input D yang diberikan.

Tabel Kebenaran D Flip Flop dengan clock

| Clock | D | Q |

|---|---|---|

| 0 | X* | NC |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

X adalah nilai 0 atau 1.

D Flip Flop dengan Pemicu Tepi

Sekarang kita akan membahas Jenis D Flip Flop yang paling umum. Apa yang diperlukan oleh sebuah komputer praktis adalah rangkaian D flip flop yang dapat melakukan pencuplikan bit data pada waktu tertentu.

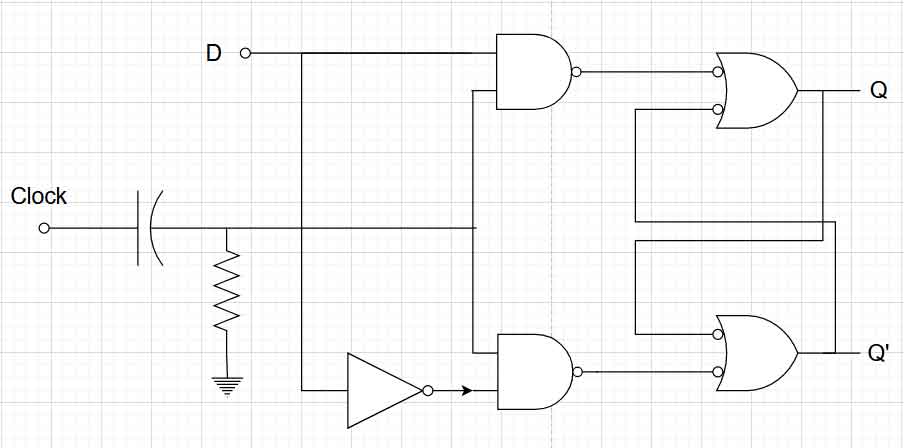

Gambar Clocked D Flip Flop dengan Pemicu Tepi

Pada gambar Clocked D FF dengan pemicu sisi tepi (sisi naik), terlihat rangkaian RC (Resistor dan Kapasitor) pada input clock. Rangkaian RC tersebut didesain sehingga konstanta waktu RC jauh lebih kecil dari pulsa sinyal clock. Oleh sebab itu kapasitor dapat mengisi muatan sepenuhnya sewaktu clock bertransisi naik.

Tegangan positif yang tajam pada clock akibat pengisian muatan dari kapasitor akan mengaktifkan gerbang-gerbang masukkan dalam waktu singkat. Jadi pengaktifan gerbang-gerbang masukkan akan terjadi ketika terjadi transisi sisi naik pada clock. Hal seperti ini bisa dilihat pada tabel dan digram waktu(timming) D Flip Flop pada pemicuan tepi.

Sedangkan transisi sisi negatif / turun, tidak menimbulkan perubahan apapun pada keluaran. Hal ini dapat dikatakan bahwa, data disimpan hanya pada sisi naik (positif).

Gambar Diagram waktu Clock D Flip Flop dengan Pemicu Tepi

Tabel Clock D Flip FLop dengan Pemicu Tepi

| Clock | D | Q |

|---|---|---|

| 0 | X | NC |

| ↑ | X | NC |

| ↓ | X | NC |

| ↑ | 0 | 0 |

| ↑ | 1 | 1 |

Preset dan Clear pada D Flip Flop

Ketika catu daya sebuah komputer dinyalakan, flip flop akan menempati keadaan yang acak (tidak menentu), sehingga penekanan tombol reset dibutuhkan saat akan mengawali operasi sebuah komputer. Dengan ini dibutuhkan sebuah sinyal clear (reset) yang dikirimkan ke semua rangkaian flip flop yang terdapat pada komputer. Di samping itu dibutuhkan juga sinyal preset (“set”) untuk mengaktifkan flip flop tertentu sebelum komputer bekerja.

| PRESET | CLEAR | CLOCK | D | Q |

|---|---|---|---|---|

| 0 | 0 | X | X | * |

| 0 | 1 | X | X | 1 |

| 1 | 0 | X | X | 0 |

| 1 | 1 | 0 | X | NC |

| 1 | 1 | ↑ | X | NC |

| 1 | 1 | ↓ | X | NC |

| 1 | 1 | ↑ | 0 | 0 |

| 1 | 1 | ↑ | 1 | 1 |

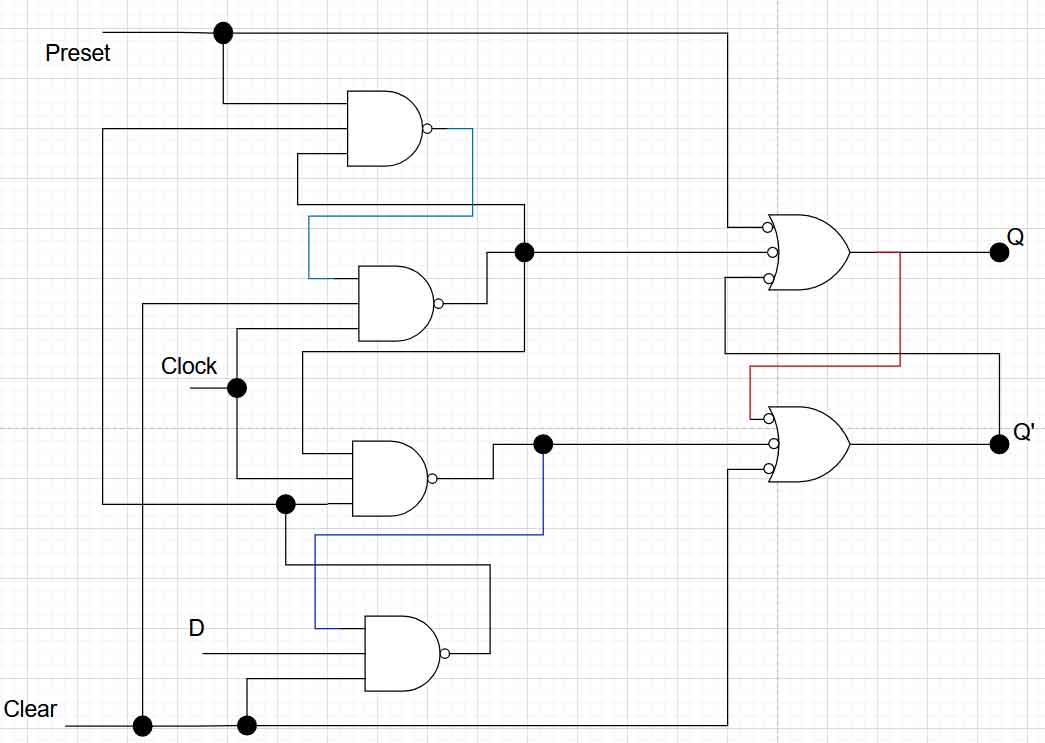

Flip Flop D Pemicu Tepi Gandeng Langsung

Rangkaian Flip Flop D ini hanya menggunakan gerbang logika NAND dan tidak menggunakan menggunakan kapasitor. Rangkaian ini hanya memberikan tanggapan terhadap sinyal input masukkan selama beberapa saat selama terjadi sinyal transisi dari rendah ke tinggi. Bit data disimpan hanya pada waktu terjadinya transisi naiknya sinyal clock.

Simbol Logika

Gambar di bawah merupakan simbol logika Flip Flop D Pemicu Tepi Gandeng Langsung. Pada simbol tersebut terdapat input di antaranya D, CLK, PR, CLR dan output di antaranya Q dan Q’. Pada input CLK (Clock) yang digambarkan dengan tanda segitiga kecil. Sedangkan bulat kecil pada PR (Preset) dan CLR (Clear) memberikan arti bahwa masukkan tersebut diinvers, sehingga masukkan bernilai rendah (0) yang akan mengaktifkan D FF ini.

Pada D FF pemicuan Tepi Gandeng Langsung terdapat tiga waktu operasi yaitu:

- Waktu Tunda Propagasi

Komponen seperti dioda dan transistor tidak dapat berubah keadaan secara sesaat (nyala atau mati). Diperlukan beberapa saat waktu untuk menyalakan dan mematikan komponen tersebut. Untuk dioda dan transistor bipolar dibutuhkan waktu dalam orde nano detik untuk switching (ON dan OFF). Jadi waktu penyaklaran adalah waktu propagasi tp. Jadi waktu propagasi ini merupakan selang waktu untuk menghasilkan perubahan output suatu gerbang atau flip flop.

Misalnya jika diketahui waktu propagasi tp sebesar 20 ns, ini artinya dibutuhkan waktu sebesar 20 ns oleh keluaran gerbang merubah keadaannya sesudah input D FF ditrigger oleh sinyal clock. Dalam banyak kasus waktu tunda ini sering diabaikan karena orde waktunya yang sangat kecil. Namun dalam rangkaian yang membutuhkan kecepatan tinggi, kecepatan waktu propagasi ini ikut menentukan.

Bayangkan saja jika sebuah rangkaian dengan kecepatan tinggi harus menunggu waktu propagasi yang lama, tentu saja hal tersebut akan mempengaruhi kecepatan rangkaian tersebut.

- Waktu Siap

Stray capasitance atau kapasitansi yang tidak diinginkan dalam sebuah rangkaian yang terjadi pada input D (dan juga faktor lain yang terjadi) mengakibatkan bit data D berada pada input sebelum terjadinya clock pada rangkaian. Waktu siap atau waktu setup (tsetup) adalah selang waktu minimum terdapatnya data pada masukkan (input) sebelum datanya clock.

Jika sebuah rangkaian D flip flop tercantum data tsetup sebesar 20 ns, maka artinya bit data akan disimpan harus berada pada input D minimum 20 ns sebelum terjadinya clock. Jika tidak, maka data bit tersebut tidak dapat terjamin pencuplikan dan peyimpanan data bit tersebut.

- Waktu Tahan

Waktu tahan adalah waktu yang mana bit data harus ditahan selama selang waktu yang agak panjang bagi transistor internal untuk berubah keadaan. Bit data D hanya diperbolehkan berubah keadaan setelah transisi selesai. Waktu tahan atau hold time (thold) adalah selang waktu minimum bit data bertahan setelah terjadinya clock pada flip flop.

Contohnya, jika diketahui besarnya tsetup 20ns dan thold 10ns, maka artinya bit data harus berada pada input D minimum 20ns sebelum terjadinya clock dan bit data harus tetap bertahan dalam input tersebut paling lama 10 ns setelah sinyak clock selesai.